Intel Nova Lake-S Rumors: Up to 288MB bLLC Cache and 52 Cores Could Challenge AMD in 2026

Wednesday, December 24, 2025Intel Nova Lake-S Rumors: Up to 288MB bLLC Cache and 52 Cores Could Challenge AMD in 2026

Intel's next-generation Nova Lake-S desktop architecture is creating huge excitement in the gaming and hardware world, with recent leaks pointing to massive advancements in core counts and cache technology. Industry sources suggest that Nova Lake-S flagships could feature up to 52 cores and a whopping 288MB of Big Last Level Cache (bLLC) in dual-tile configurations—positioning Intel to directly counter AMD's upcoming Zen 6 processors and reclaim ground in both gaming and productivity.

Conceptual view of advanced Intel multi-tile CPU design (similar to rumored Nova Lake-S)

Speculated Nova Lake-S multi-tile configuration with integrated bLLC

Intel's Push for Bigger Cache: Introducing bLLC

For years, AMD's 3D V-Cache has dominated gaming performance by stacking extra L3 cache to reduce latency in demanding titles. Current Arrow Lake CPUs top out at modest L3 sizes, but Nova Lake-S rumors indicate Intel's response: a Big Last Level Cache (bLLC) integrated into compute tiles, scaling massively to compete head-on.

Unlike AMD's vertical stacking, bLLC is rumored to be on-die or closely integrated, potentially offering lower latency access across P-cores, E-cores, and even LP-E-cores. This could minimize memory bottlenecks in high-frame-rate gaming and threaded workloads.

Illustration of advanced Intel cache allocation concepts

Breaking Down the Latest Nova Lake-S Rumors

Recent leaks outline unlocked K-series SKUs with bLLC across four main configurations. Dual-tile flagships aim for extreme performance, while single-tile models target gaming and mid-range:

| Configuration | Example SKU | Cores (P + E + LP-E) | bLLC Cache | Total Potential L3 |

|---|---|---|---|---|

| Dual-Tile Flagship | Core Ultra 9 equivalent | 16 + 32 + 4 = 52 | 144MB per tile | 288MB |

| Dual-Tile High-End | Core Ultra 9 equivalent | 14 + 24 + 4 = 42 | 144MB per tile | 288MB |

| Single-Tile Mid-Range | Core Ultra 7 equivalent | 8 + 16 + 4 = 28 | 144MB | 144MB |

| Single-Tile Mainstream | Core Ultra 7 equivalent | 8 + 12 + 4 = 24 | 144MB | 144MB |

| Arrow Lake (for comparison) | Core Ultra 9 285K | 8 + 16 = 24 | None | 36MB |

Nova Lake-S is expected to use advanced nodes (TSMC/Intel mix), new Coyote Cove P-cores and Arctic Wolf E-cores, with ~15% IPC gains rumored for P-cores. The platform shifts to LGA 1954 socket.

Head-to-Head with AMD Zen 6

The timing aligns perfectly with AMD's Zen 6 launch in 2026. Recent rumors show both companies targeting similar 288MB cache figures—AMD via dual 3D V-Cache, Intel via dual bLLC tiles. This sets up an intense "cache war" for gaming dominance in titles like Cyberpunk 2077 and Flight Simulator.

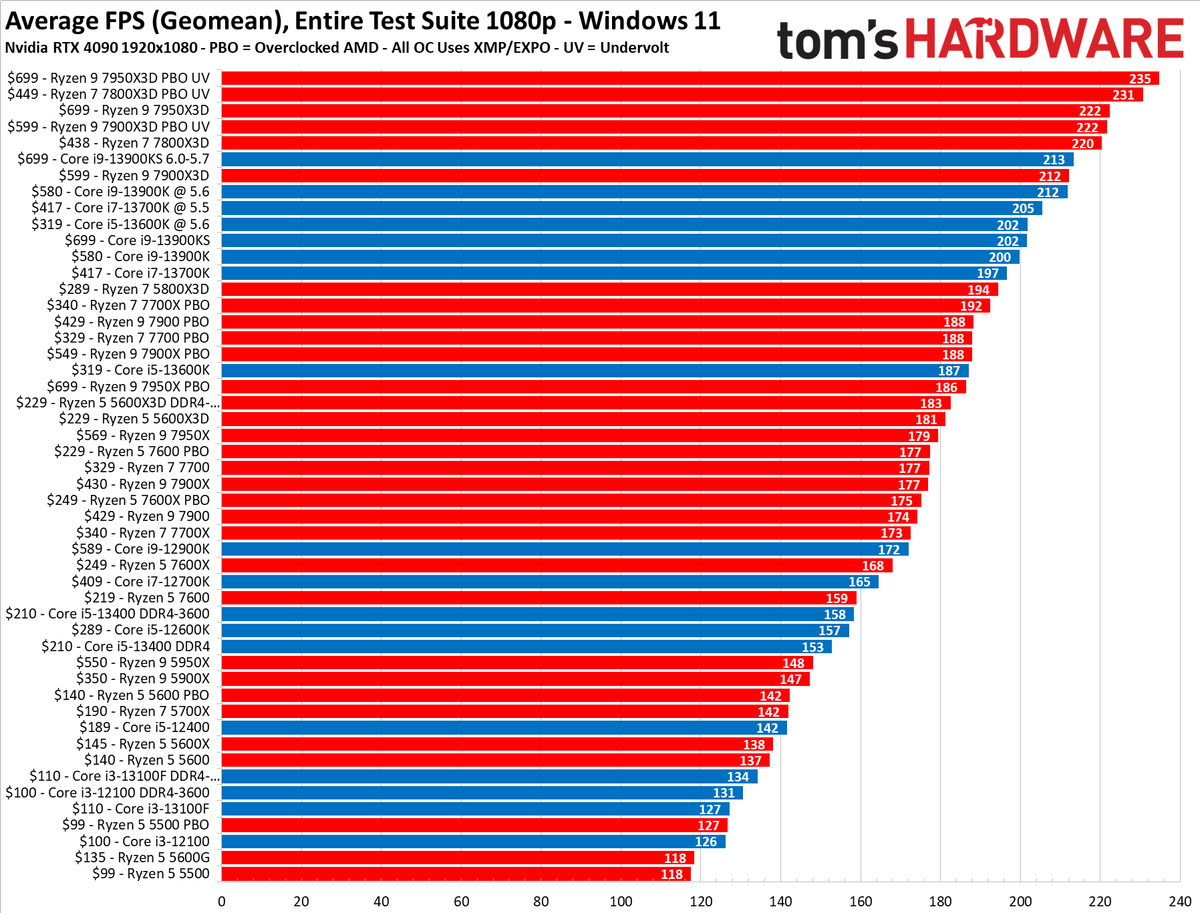

2025 CPU gaming hierarchy – Nova Lake could close the gap

Intel's higher core counts favor productivity, while massive cache could boost gaming consistency. Expected IPC uplifts and process improvements will amplify gains for both sides.

Why Massive Cache and Cores Matter

Huge L3/bLLC keeps more data on-chip, delivering:

- Higher FPS and smoother 1% lows in games

- Better performance in ray-traced and open-world titles

- Superior multi-threaded productivity and content creation

Challenges include higher costs for large cache dies (some reports warn of "prohibitively expensive" pricing for top-tier models), potential thermal/power limits, and platform changes requiring new motherboards.

Community anticipation is high, with discussions around reclaiming gaming leadership and extreme overclocking potential.

Outlook: Cache Wars Intensify in 2026

If these rumors hold, Nova Lake-S could mark Intel's strong comeback, offering unprecedented scale for gaming and pro workloads. With AMD matching cache ambitions, 2026 promises fierce competition and big leaps forward.

Stay tuned for official details—leaks often precede reveals at CES or Computex. What do you think of Nova Lake-S potential? Share in the comments!